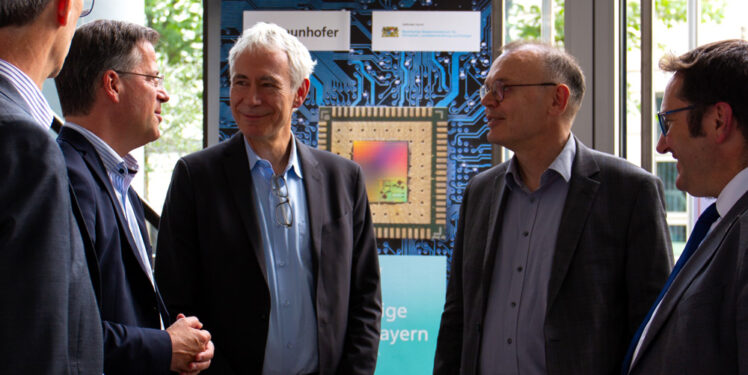

VDE-Fachgruppe »Vertrauenswürdige Elektronik« gegründet

Die neue VDE-Fachgruppe »Vertrauenswürdige Elektronik«, gegründet von der Forschungsplattform »Velektronik« und dem Verband der Elektrotechnik, Elektronik und Informationstechnik e.V (VDE), wird als zentrale Anlaufstelle das Thema »Vertrauenswürdige Elektronik« im Verbund von Industrie, Forschung und Behörden in Deutschland vorantreiben.